DAY6

✅ RISC-V

UC버클리에서 개발중인 무료 오픈소스 RISC 명령어셋 아키텍처

명령어 길이가 모두 32bit로 동일

✅ Single-Cycle Architecture

- 특징 : 모든 명령어가 (1CLK) 내에 동작.

- 장점 : 구조가 매우 simple하다.

- 단점 : 한 클럭 내에 동작해야되기 때문에 느리다.

✅ Multi-Cycle Architecture

- 특징 : 명령어 Type별 동작 CLK 수가 다르다.

- 장점 : Single-Cycle보다는 조금 빠르다.

- 단점 : Single-Cycle보다 구조가 조금 복잡하다.

✅ Pipe-Line Architecture

- 특징 : 모든 명령어가 (1CLK) 내에 동작.

- 장점 : Single-Cycle보다 많이 빠르다.

- 단점 : Single-Cycle보다 구조가 많이 복잡하다.

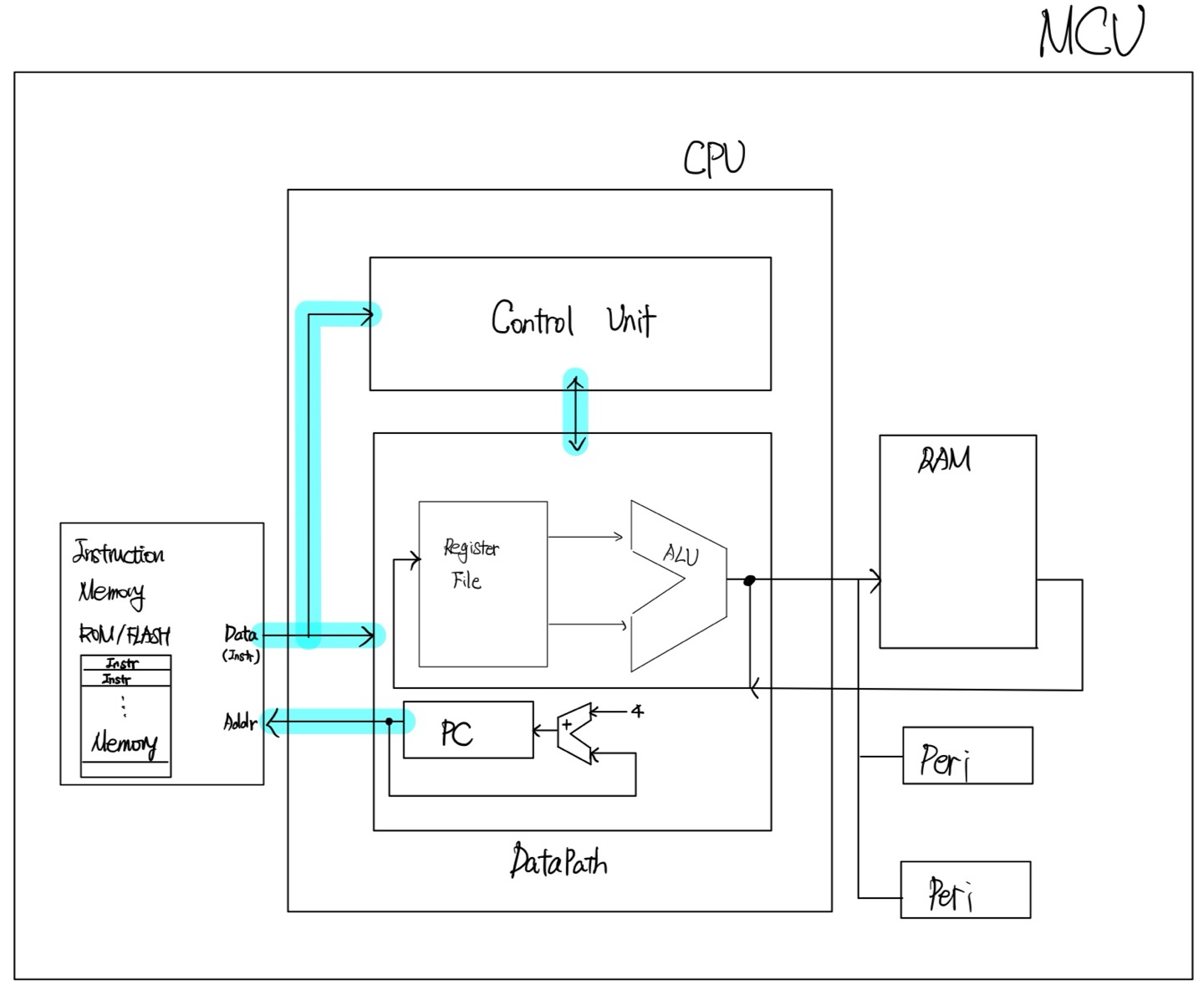

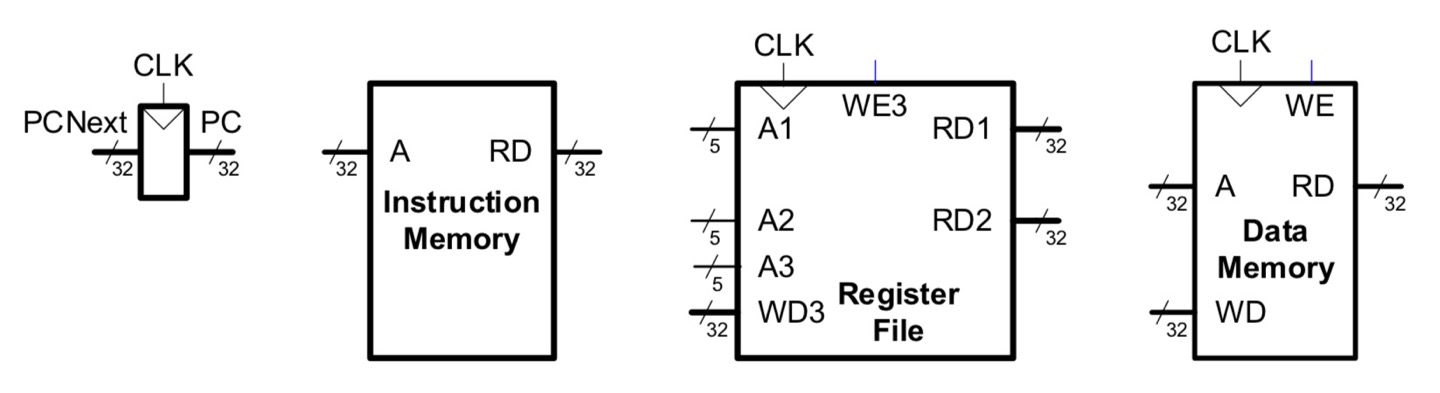

✅ CPU 기본 모듈 (하버드 구조)

- RegisterFile

- ALU

- ROM/Flash(Instruction Memory)

- RAM(DataMemory)

- PC(Program Counter)

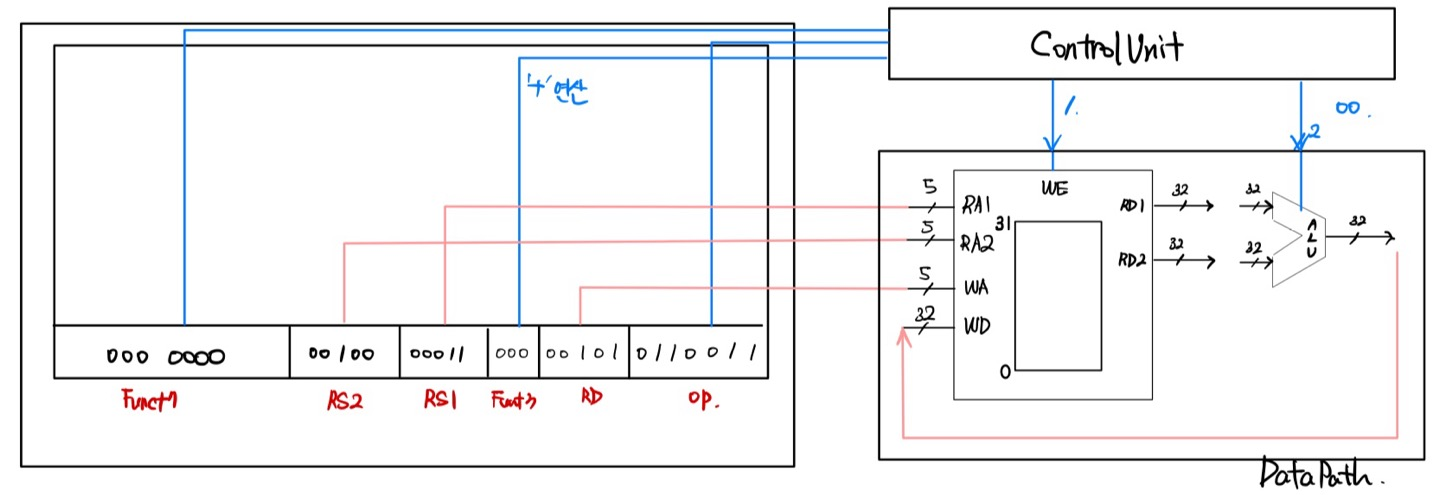

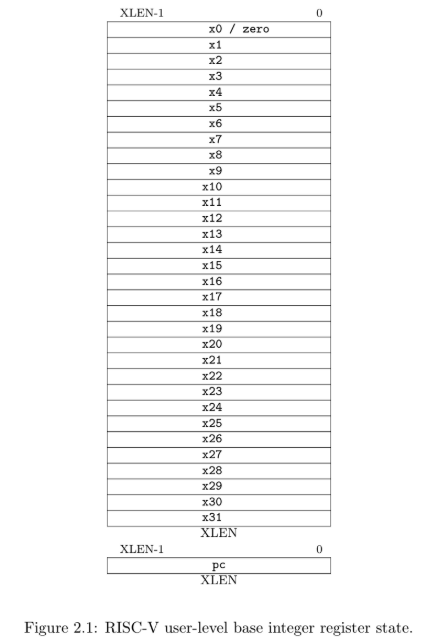

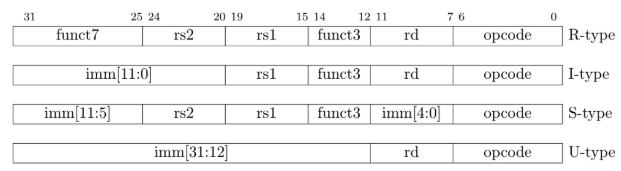

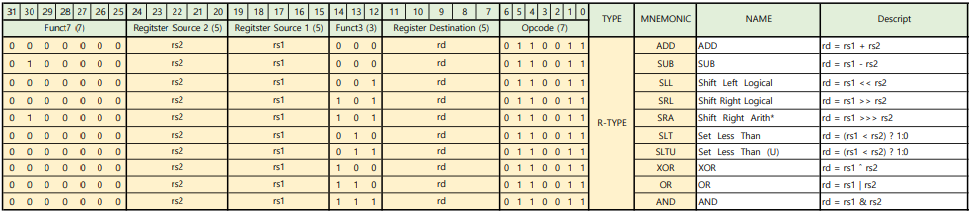

✅ RV32I_R_Type

Funct7 RS2 RS1 Funct3 RD OP

machine code의 값이 이렇게 되어있음.

R-Type의 opcode는 다 같음 -> Type마다 opcode는 같음.

Funct3 어떤 연산인지를 선택할 수 있음.

💡 연습

ADD X5, X3, X4

Funct7 = 7’d0 RS2 = 5’d4 RS1 = 5’d3 Funct3 = 3’d0 RD = 5’d5 OpCode = 7’b0110011